# 10G PON Chipset

10G PON Chipset PRX126 (PRX126B0BI)

10G PON Chipset PRX126 (PRX126B1BI)

10G PON Chipset PRX126 (PRX126B2BI)

10G PON Chipset PRX126 (PRX126B3BI-AV-T)

Position Restriction 2013 of Arming Strong Control of Strong Contr

## **Data Sheet**

**MaxLinear Confidential**

Revision 3.6, 2023-02-13 Reference ID 617963

### Legal Notice

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. MaxLinear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

MaxLinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, any MaxLinear trademarks (MxL, Full-Spectrum Capture, FSC, G.now, AirPHY, Puma, and AnyWAN), and the MaxLinear logo on the products sold are all property of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved.

\*Other company trademarks and product names appearing herein are the property of their respective owners.

© 2023 MaxLinear, Inc. All rights reserved.

MaxLinear, Inc. 5966 La Place Court, Suite 100 Carlsbad, CA 92008

Tel.: +1 (760) 692-0711 Fax: +1 (760) 444-8598 www.maxlinear.com

#### **Revision History**

| Current: Previous:                    | Revision 3.6, 2023-02-13<br>Revision 3.5, 2022-09-08                                                                 |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| Page Major changes since Revision 3.5 |                                                                                                                      |

| All                                   | Added PRX126B3BI to the scope of the document.                                                                       |

| 12                                    | Updated Chapter 1.3 Differences between Silicon Steps.                                                               |

| 88                                    | Updated Chapter 20 Chip ID.                                                                                          |

| 119                                   | Updated Chapter 24.1 Chip Identification and Ordering Information. Removed ordering codes for the B0 and B1 devices. |

| 124                                   | Updated Literature References.                                                                                       |

Position Assistated position as a strain and a strain and

#### **Table of Contents**

| 1               | Overview                                                                                                                                                                                                                                                          | . 11 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

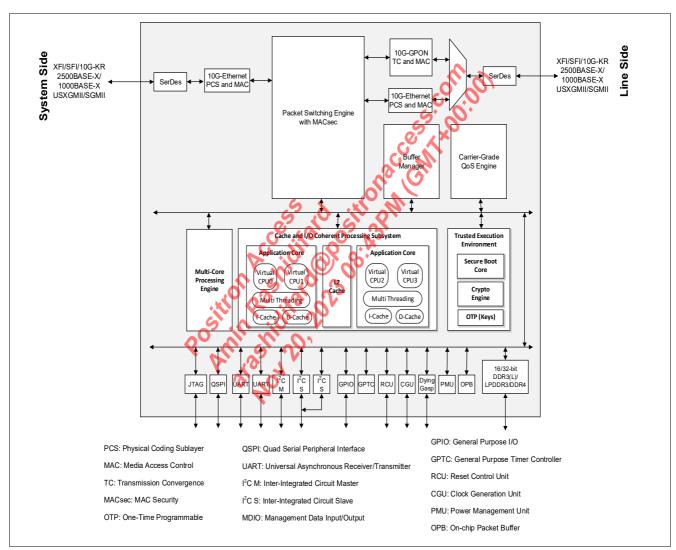

| 1.1             | Block Diagram                                                                                                                                                                                                                                                     | . 11 |

| 1.2             | Features                                                                                                                                                                                                                                                          | . 12 |

| 1.3             | Differences between Silicon Steps                                                                                                                                                                                                                                 | . 12 |

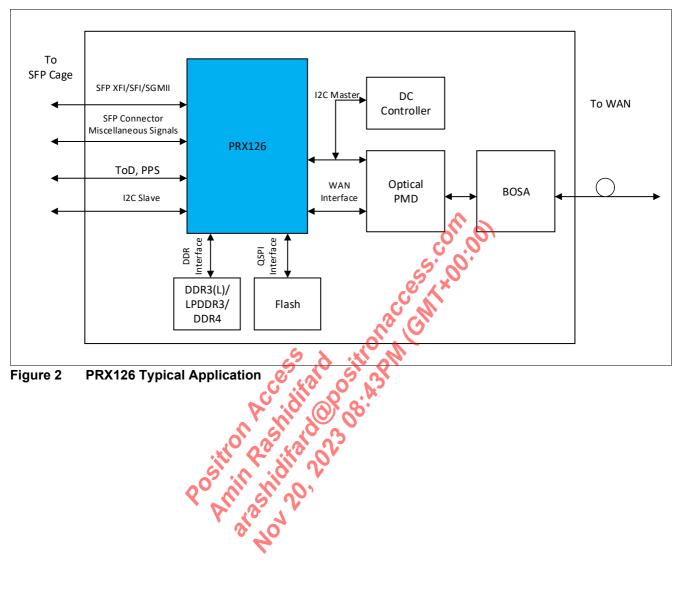

| 1.4             | Typical Application                                                                                                                                                                                                                                               | . 13 |

| 2               | Pin Descriptions                                                                                                                                                                                                                                                  | 14   |

| _<br>2.1        | List of Interfaces                                                                                                                                                                                                                                                |      |

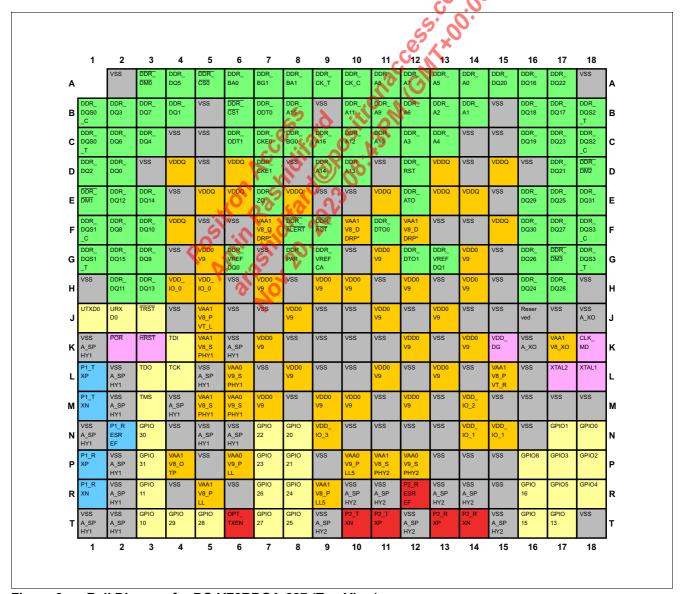

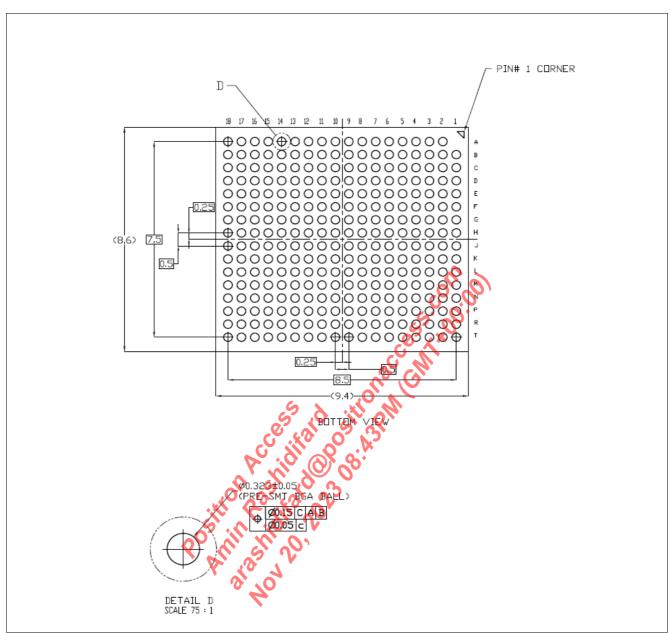

| 2.2             | Ball Diagram                                                                                                                                                                                                                                                      |      |

| 2.3             | Ball (Pin) Function Descriptions                                                                                                                                                                                                                                  |      |

| 2.3.1           | WAN Signals                                                                                                                                                                                                                                                       |      |

| 2.3.2           | SFP XFI/SFI/SGMII Signals                                                                                                                                                                                                                                         |      |

| 2.3.3           | SFP Connector Miscellaneous Signals                                                                                                                                                                                                                               |      |

| 2.3.4           | _                                                                                                                                                                                                                                                                 |      |

| 2.3.5           | UART Signals  QSPI Signals  I <sup>2</sup> C Signals  Clock Signals  General Purpose I/O Signals  JTAG Signals  DDR-SDRAM Signals  Reset Signals  Power Supply  Ground  Dying Gasp  Reserved Signals  Digital Signal Ball (Pin) Reset Property and Drive Strength | . 21 |

| 2.3.6           | I <sup>2</sup> C Signals                                                                                                                                                                                                                                          | . 21 |

| 2.3.7           | Clock Signals                                                                                                                                                                                                                                                     | 22   |

| 2.3.8           | General Purpose I/O Signals                                                                                                                                                                                                                                       | 22   |

| 2.3.9           | JTAG Signals                                                                                                                                                                                                                                                      | 24   |

| 2.3.10          | DDR-SDRAM Signals                                                                                                                                                                                                                                                 | 25   |

| 2.3.11          | Reset Signals                                                                                                                                                                                                                                                     | . 28 |

| 2.3.12          | Power Supply                                                                                                                                                                                                                                                      | . 28 |

| 2.3.13          | Ground                                                                                                                                                                                                                                                            | . 29 |

| 2.3.14          | Dving Gasp                                                                                                                                                                                                                                                        | . 30 |

| 2.3.15          | Reserved Signals                                                                                                                                                                                                                                                  | . 30 |

| 2.4             | Digital Signal Ball (Pin) Reset Property and Drive Strength                                                                                                                                                                                                       | . 31 |

| 2.4.1           | Reset Property and Drive Strength of Peripherals and General Purpose I/O                                                                                                                                                                                          |      |

| 2.4.2           | Reset Property and Drive Strength of UART0 Signals                                                                                                                                                                                                                |      |

| 2.4.3           | Reset Property and Drive Strength of Reset Signals                                                                                                                                                                                                                |      |

| 2.4.4           | Reset Property and Drive Strength of OPT_TXEN Signal                                                                                                                                                                                                              |      |

| 2.4.5           | Reset Property and Drive Strength of JTAG Signals                                                                                                                                                                                                                 |      |

| 2.5             | Strap Pin Configuration                                                                                                                                                                                                                                           |      |

| 3               | Data Path                                                                                                                                                                                                                                                         |      |

| <b>ა</b><br>3.1 | Data Path Components                                                                                                                                                                                                                                              |      |

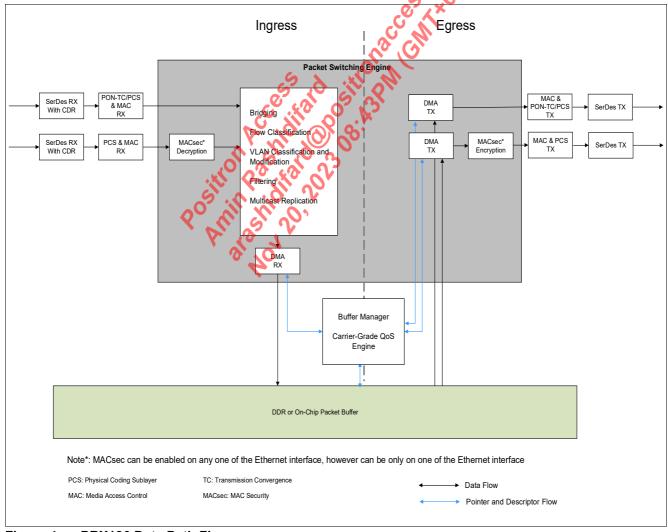

| 3.1<br>3.2      | Data Path Flow                                                                                                                                                                                                                                                    |      |

| 3.2.1           | Fast Path Data Flow                                                                                                                                                                                                                                               |      |

| 3.2.1<br>3.2.2  | CPU Path Data Flow                                                                                                                                                                                                                                                |      |

| 3.2.2           |                                                                                                                                                                                                                                                                   |      |

| 4               | SerDes                                                                                                                                                                                                                                                            |      |

| 4.1             | SerDes Instances                                                                                                                                                                                                                                                  | _    |

| 4.2             | WAN SerDes                                                                                                                                                                                                                                                        |      |

| 4.3             | XFI SerDes                                                                                                                                                                                                                                                        | . 41 |

| 5               | Ethernet Physical Coding Sublayer                                                                                                                                                                                                                                 | . 42 |

| 6               | Ethernet MAC                                                                                                                                                                                                                                                      | . 43 |

| 7               | PON Subsystem                                                                                                                                                                                                                                                     | . 44 |

| 8               | Packet Switching Engine                                                                                                                                                                                                                                           | . 45 |

| 8.1             | Features                                                                                                                                                                                                                                                          |      |

| 8.2             | Functional Description                                                                                                                                                                                                                                            | . 47 |

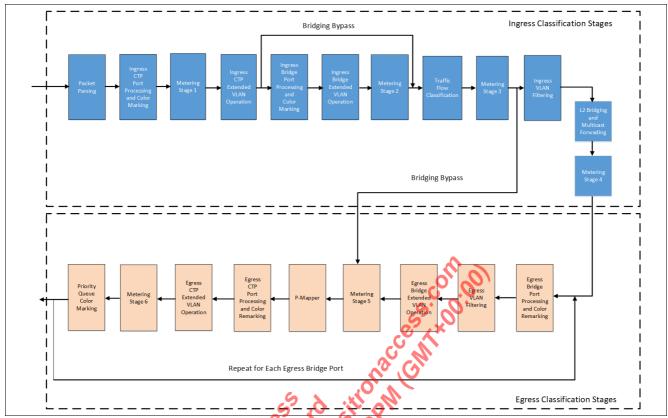

| 8.2.1<br>8.2.2<br>8.2.3                                                                                                                                                             | ITU-T G.988 OMCI L2 MAC Bridge Reference Model                                                                                                                                                                                                                                                                                                                                               | 47                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

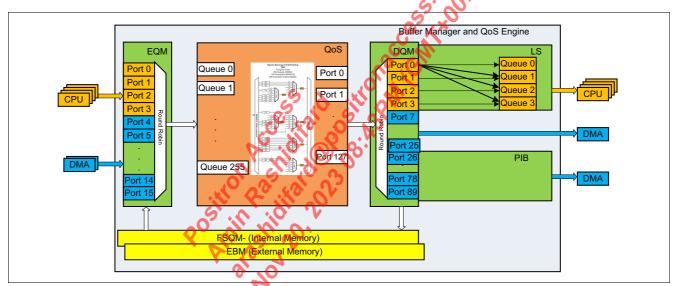

| 9                                                                                                                                                                                   | Buffer Manager                                                                                                                                                                                                                                                                                                                                                                               | 53                                                                         |

| 9.1                                                                                                                                                                                 | Buffer Manager Overview                                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

| 9.2                                                                                                                                                                                 | Enqueue Manager                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 9.2<br>9.3                                                                                                                                                                          | Dequeue Manager                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 9.4                                                                                                                                                                                 | Free Buffer Manager                                                                                                                                                                                                                                                                                                                                                                          |                                                                            |

| 9. <del>4</del><br>9.5                                                                                                                                                              | Load Spreader Overview                                                                                                                                                                                                                                                                                                                                                                       |                                                                            |

| 9.5<br>10                                                                                                                                                                           | Carrier Grade Quality of Service Engine                                                                                                                                                                                                                                                                                                                                                      |                                                                            |

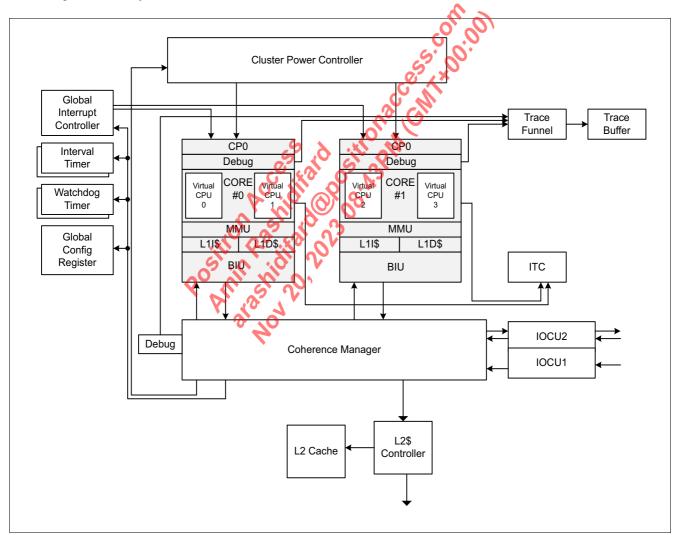

| 11                                                                                                                                                                                  | Coherent Processing Subsystem                                                                                                                                                                                                                                                                                                                                                                |                                                                            |

| 11.1                                                                                                                                                                                | InterAptiv* Processor                                                                                                                                                                                                                                                                                                                                                                        |                                                                            |

| 11.1.1<br>11.1.1                                                                                                                                                                    | Virtual CPU                                                                                                                                                                                                                                                                                                                                                                                  |                                                                            |

| 11.1.1                                                                                                                                                                              | Thread Context                                                                                                                                                                                                                                                                                                                                                                               |                                                                            |

| 11.1.2                                                                                                                                                                              | Evacution Unit                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                         |

| 11.1.3<br>11.1.4                                                                                                                                                                    | Execution Unit                                                                                                                                                                                                                                                                                                                                                                               | 50                                                                         |

| 11.1.4                                                                                                                                                                              | System Central Congressor CD0                                                                                                                                                                                                                                                                                                                                                                | 50                                                                         |

| 11.1.5<br>11.1.6                                                                                                                                                                    | Mamary Management Unit                                                                                                                                                                                                                                                                                                                                                                       | 50                                                                         |

|                                                                                                                                                                                     | Sycantian Landing                                                                                                                                                                                                                                                                                                                                                                            | 59                                                                         |

| 11.1.7                                                                                                                                                                              | Calcarate Manager Committee                                                                                                                                                                                                                                                                                                                                                                  | 59                                                                         |

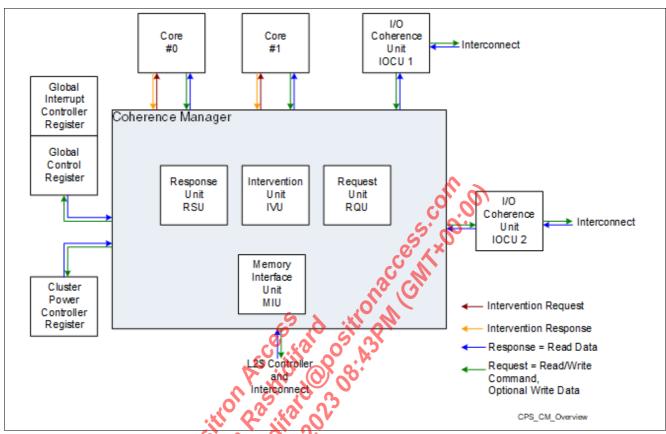

| 11.2                                                                                                                                                                                | La Casha Overview                                                                                                                                                                                                                                                                                                                                                                            | 64                                                                         |

| 11.3                                                                                                                                                                                | L2 Cache Attributes                                                                                                                                                                                                                                                                                                                                                                          | 01                                                                         |

| 11.3.1                                                                                                                                                                              | L2 Cache Attributes                                                                                                                                                                                                                                                                                                                                                                          | 01                                                                         |

| 11.3.2                                                                                                                                                                              | L2 Cache Protocols                                                                                                                                                                                                                                                                                                                                                                           | 67                                                                         |

| 11.4                                                                                                                                                                                | TO Conference Office                                                                                                                                                                                                                                                                                                                                                                         | 02                                                                         |

|                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                            |

| 12                                                                                                                                                                                  | Boot/TEP Secure Boot Core 💛 📣                                                                                                                                                                                                                                                                                                                                                                | 63                                                                         |

| 12.1                                                                                                                                                                                | MIPS 4KEc* Features                                                                                                                                                                                                                                                                                                                                                                          | 63                                                                         |

|                                                                                                                                                                                     | MIPS 4KEc* Features Secure Boot Core UART                                                                                                                                                                                                                                                                                                                                                    | 63<br>64                                                                   |

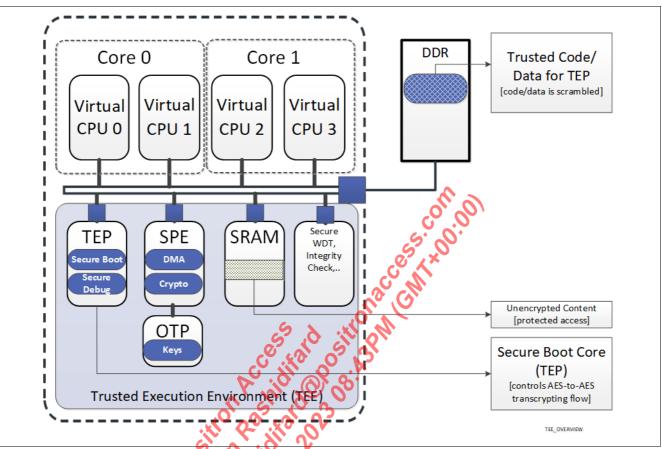

| 12.1                                                                                                                                                                                | MIPS 4KEc* Features Secure Boot Core UART Trusted Execution Environment                                                                                                                                                                                                                                                                                                                      | 63<br>63<br>64<br>65                                                       |

| 12.1<br>12.2                                                                                                                                                                        | MIPS 4KEc* Features Secure Boot Core UART Trusted Execution Environment Features                                                                                                                                                                                                                                                                                                             | 63<br>64<br>65<br>65                                                       |

| 12.1<br>12.2<br><b>13</b>                                                                                                                                                           | MIPS 4KEc* Features Secure Boot Core UART  Trusted Execution Environment Features TEP Access to Platform Resource                                                                                                                                                                                                                                                                            | 63<br>64<br>65<br>65<br>66                                                 |

| 12.1<br>12.2<br><b>13</b><br>13.1                                                                                                                                                   | Execution Unit  Multiply/Divide Unit  System Control Co-processor CP0  Memory Management Unit  Exception Handling  Coherence Manager Overview  L2 Cache Overview  L2 Cache Attributes  L2 Cache Protocols  IO Coherence Unit  Boot/TEP Secure Boot Core  MIPS 4KEc* Features  Secure Boot Core UART  Trusted Execution Environment  Features  TEP Access to Platform Resource  Root of Trust | 66                                                                         |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2                                                                                                                                           | Root of Trust                                                                                                                                                                                                                                                                                                                                                                                | 66<br>66                                                                   |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1                                                                                                                                 | Root of Trust                                                                                                                                                                                                                                                                                                                                                                                | 66<br>66                                                                   |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2                                                                                                                       | Root of Trust                                                                                                                                                                                                                                                                                                                                                                                | 66<br>66                                                                   |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3                                                                                                             | Root of Trust  Access Protection  InterAptiv* CPU Cluster Initial ID Adaptation                                                                                                                                                                                                                                                                                                              | 66<br>66<br>67                                                             |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3                                                                                                     | Root of Trust  Access Protection  InterAptiv* CPU Cluster Initial ID Adaptation  Interconnect Protection Mechanism                                                                                                                                                                                                                                                                           | 66<br>66<br>67<br>67                                                       |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1                                                                                                   | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification                                                                                                                                                                                                                                                               | 66<br>66<br>67<br>67                                                       |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1<br>13.3.1                                                                                         | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview                                                                                                                                                                                                                                           | 66<br>66<br>67<br>67<br>67                                                 |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.3.3<br>13.3.1<br>13.3.2<br>13.3.3                                                                               | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software                                                                                                                                                                                                                 | 66<br>66<br>67<br>67<br>67<br>68                                           |

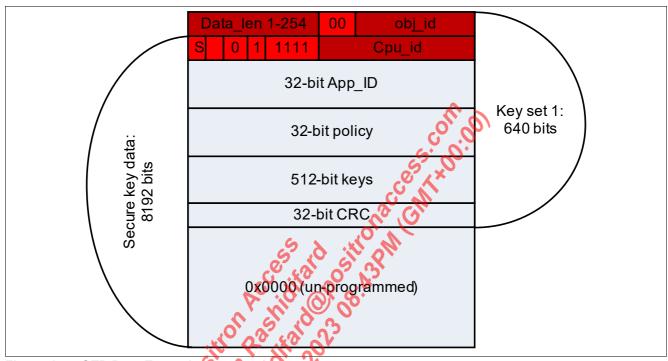

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.3.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1                                                             | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory                                                                                                                                                                               | 66<br>66<br>67<br>67<br>67<br>68<br>68                                     |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.3.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1                                                             | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System                                                                                                                                                                  | 66<br>66<br>67<br>67<br>67<br>68<br>68<br>70                               |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3<br>13.                                                                                              | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features                                                                                                                                                         | 666<br>666<br>677<br>677<br>678<br>688<br>70                               |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br><b>14</b>                                                | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description                                                                                                                                  | 666<br>666<br>677<br>677<br>686<br>6870<br>7071                            |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br><b>14</b><br>14.1                                        | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description Boot Selection after POR                                                                                                         | 66<br>66<br>67<br>67<br>67<br>68<br>68<br>70<br>71<br>71                   |

| 12.1<br>12.2<br>13<br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br>14.1<br>14.1<br>14.2<br>14.2.1                                  | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description Boot Selection after POR  Multi-core Processing Engine                                                                           | 66<br>66<br>67<br>67<br>67<br>68<br>68<br>70<br>71<br>71                   |

| 12.1<br>12.2<br>13<br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.3.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br>14.1<br>14.2<br>14.2.1                                          | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description Boot Selection after POR  Multi-core Processing Engine MPE Features                                                              | 66<br>66<br>67<br>67<br>67<br>67<br>68<br>68<br>70<br>71<br>71<br>72<br>73 |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.2.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br><b>14</b><br>14.1<br>14.2<br>14.2.1<br><b>15</b><br>15.1 | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description Boot Selection after POR  Multi-core Processing Engine MPE Features Hardware Modules                                             | 66<br>66<br>67<br>67<br>67<br>68<br>68<br>70<br>71<br>71<br>72<br>73<br>73 |

| 12.1<br>12.2<br><b>13</b><br>13.1<br>13.2<br>13.2.1<br>13.2.2<br>13.3.3<br>13.3.1<br>13.3.2<br>13.3.3<br>13.4<br>13.4.1<br><b>14</b><br>14.1<br>14.2<br>14.2.1                      | Root of Trust Access Protection InterAptiv* CPU Cluster Initial ID Adaptation Interconnect Protection Mechanism Identification Protection Overview Interaction with Software Secure Platform Engine OTP Memory  Boot System Features Functional Description Boot Selection after POR  Multi-core Processing Engine MPE Features                                                              | 66<br>66<br>67<br>67<br>67<br>68<br>68<br>70<br>71<br>71<br>72<br>73<br>73 |

| 15.2.3       | MPE Controller                                                                                                                                                                                                                                                                                                                                                      | 74 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 15.2.4       | Coherent Memory Copy Engine                                                                                                                                                                                                                                                                                                                                         | 74 |

| 16           | DDR SDRAM Controller                                                                                                                                                                                                                                                                                                                                                | 75 |

| 16.1         | DDR SDRAM System Overview                                                                                                                                                                                                                                                                                                                                           | 75 |

| 16.2         | Memory Access Scheduler                                                                                                                                                                                                                                                                                                                                             | 76 |

| 16.2.1       | Features                                                                                                                                                                                                                                                                                                                                                            | 76 |

| 16.2.2       | QoS Arbitration and Levels                                                                                                                                                                                                                                                                                                                                          |    |

| 16.3         | DDR Universal Protocol Controller                                                                                                                                                                                                                                                                                                                                   |    |

| 16.3.1       | Features                                                                                                                                                                                                                                                                                                                                                            |    |

| 16.3.2       | Data Eye Training Control                                                                                                                                                                                                                                                                                                                                           |    |

| 16.4         | DDR PHY Utility Block                                                                                                                                                                                                                                                                                                                                               |    |

| 16.5         | DDR SDRAM PHY                                                                                                                                                                                                                                                                                                                                                       |    |

| 16.6         | SSTL IO Block                                                                                                                                                                                                                                                                                                                                                       |    |

| 16.6.1       | Features                                                                                                                                                                                                                                                                                                                                                            | 78 |

| 16.6.2       | ZQ Calibration Cell                                                                                                                                                                                                                                                                                                                                                 | 78 |

| 16.7         | DDR SDRAM Device Support                                                                                                                                                                                                                                                                                                                                            | 78 |

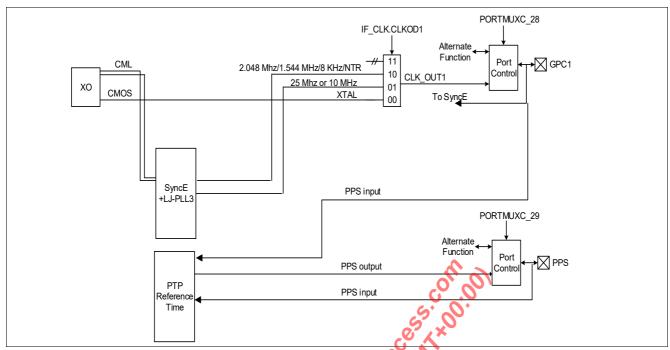

| 17           | Clock Generation Unit                                                                                                                                                                                                                                                                                                                                               | 80 |

| 17.1         | Features                                                                                                                                                                                                                                                                                                                                                            | 80 |

| 17.2         | Functional Description                                                                                                                                                                                                                                                                                                                                              | 81 |

| 17.2.1       | Clock Input Option and Oscillator Circuit                                                                                                                                                                                                                                                                                                                           | 82 |

| 17.2.2       | External Clock Output or Input Interface                                                                                                                                                                                                                                                                                                                            | 82 |

| 17.2.3       | Synchronous Ethernet                                                                                                                                                                                                                                                                                                                                                | 83 |

| 17.2.4       | Time of Day                                                                                                                                                                                                                                                                                                                                                         | 83 |

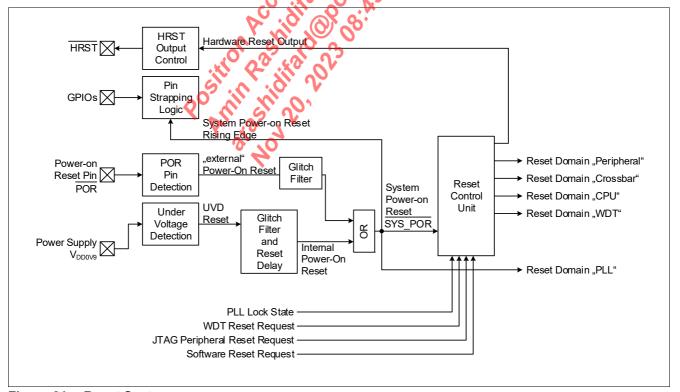

| 18           | Reset System                                                                                                                                                                                                                                                                                                                                                        | 84 |

| 18.1         | Features                                                                                                                                                                                                                                                                                                                                                            | 84 |

| 18.2         | Functional Description                                                                                                                                                                                                                                                                                                                                              | 84 |

| 18.2.1       | Overview                                                                                                                                                                                                                                                                                                                                                            | 84 |

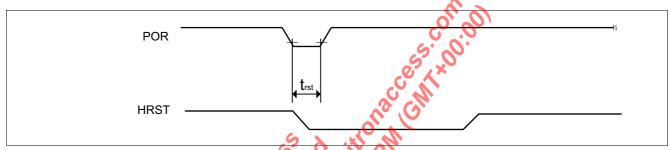

| 18.2.2       | Power-on Reset Generation 2.7                                                                                                                                                                                                                                                                                                                                       | 85 |

| 18.2.3       | Features ZQ Calibration Cell DDR SDRAM Device Support  Clock Generation Unit Features Functional Description Clock Input Option and Oscillator Circuit External Clock Output or Input Interface Synchronous Ethernet Time of Day  Reset System Features Functional Description Overview Power-on Reset Generation Hardware Reset Output Pin  Multi-Processor System | 85 |

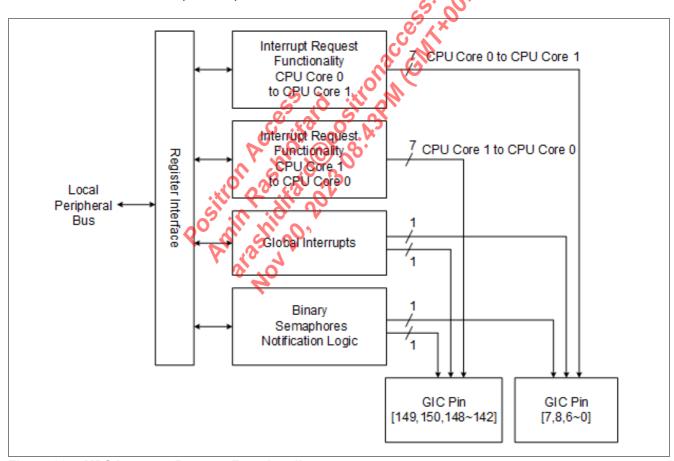

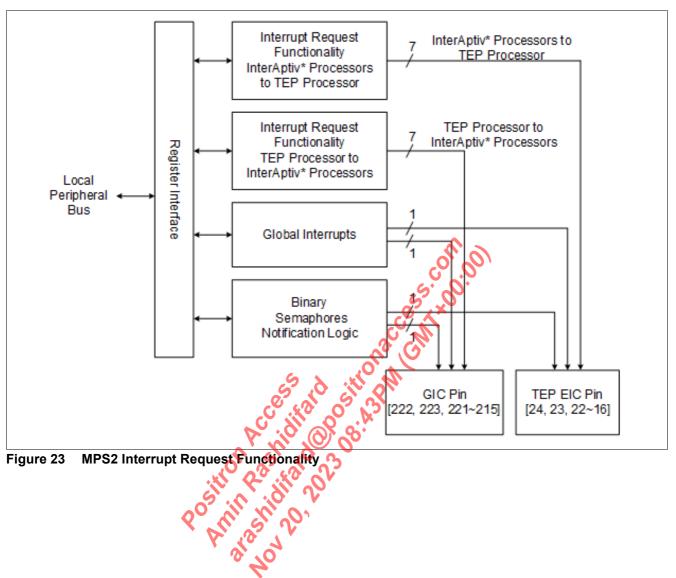

| 19           | Multi-Processor System (1) (1) (2)                                                                                                                                                                                                                                                                                                                                  | 86 |

| 20           | Chip ID                                                                                                                                                                                                                                                                                                                                                             | 88 |

| 21           | Peripherals                                                                                                                                                                                                                                                                                                                                                         | 89 |

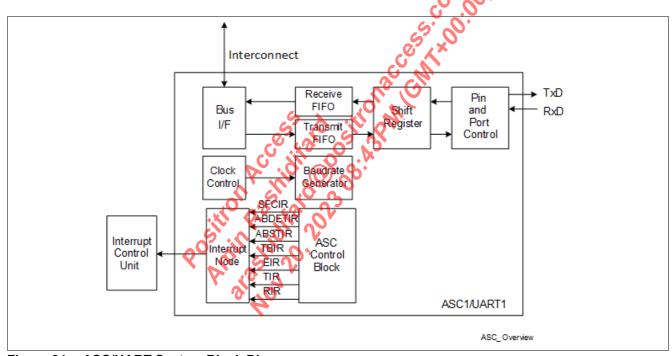

| 21.1         | Universal Asynchronous Receiver/Transmitter                                                                                                                                                                                                                                                                                                                         |    |

| 21.1.1       | Features                                                                                                                                                                                                                                                                                                                                                            | 89 |

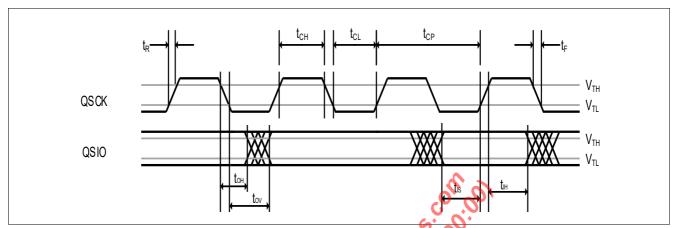

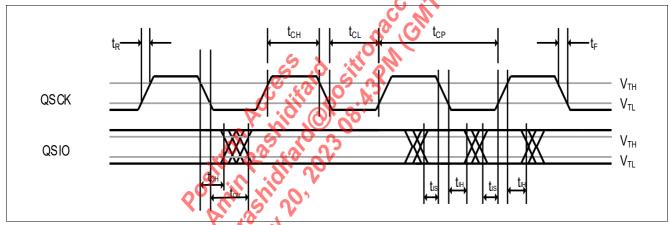

| 21.2         | Quad Serial Peripheral Interface                                                                                                                                                                                                                                                                                                                                    | 90 |

| 21.2.1       | Features                                                                                                                                                                                                                                                                                                                                                            |    |

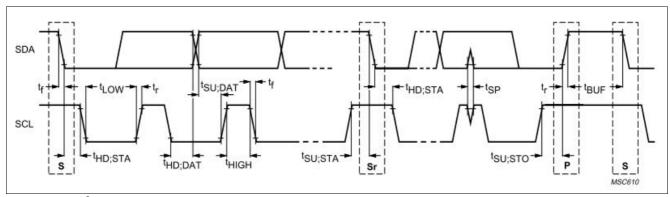

| 21.3         | I <sup>2</sup> C Controller                                                                                                                                                                                                                                                                                                                                         | 91 |

| 21.3.1       | Features                                                                                                                                                                                                                                                                                                                                                            |    |

| 21.3.2       | Features of the I <sup>2</sup> C Slave Controller                                                                                                                                                                                                                                                                                                                   |    |

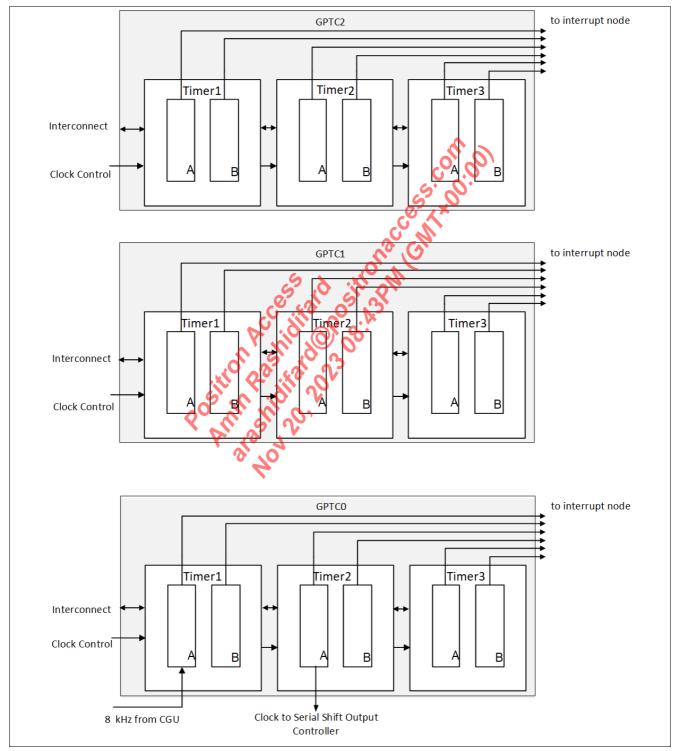

| 21.4         | General Purpose Timer Counter                                                                                                                                                                                                                                                                                                                                       |    |

| 21.4.1       | Features                                                                                                                                                                                                                                                                                                                                                            |    |

| 21.4.2       | Overview                                                                                                                                                                                                                                                                                                                                                            |    |

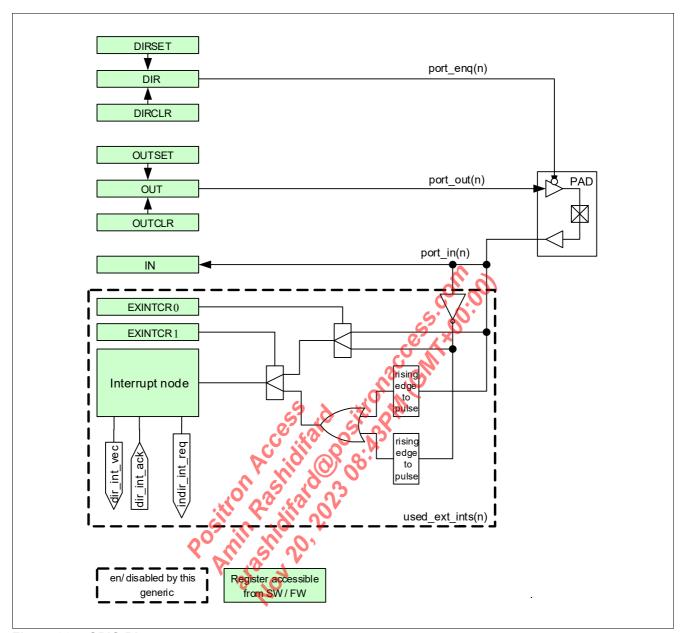

| 21.5         | General Purpose I/O                                                                                                                                                                                                                                                                                                                                                 |    |

| 21.5.1       | Features                                                                                                                                                                                                                                                                                                                                                            |    |

| 21.5.2       | GPIO Functionality                                                                                                                                                                                                                                                                                                                                                  |    |

| 21.5.3       | Pad Control Overview                                                                                                                                                                                                                                                                                                                                                |    |

| 21.5.4       | External Interface                                                                                                                                                                                                                                                                                                                                                  |    |

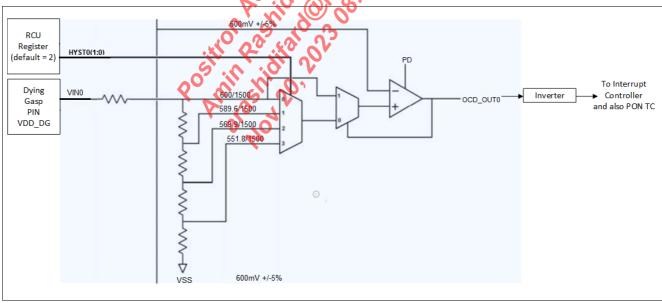

| 21.6<br>21.7 | Dying Gasp Detection Module                                                                                                                                                                                                                                                                                                                                         |    |

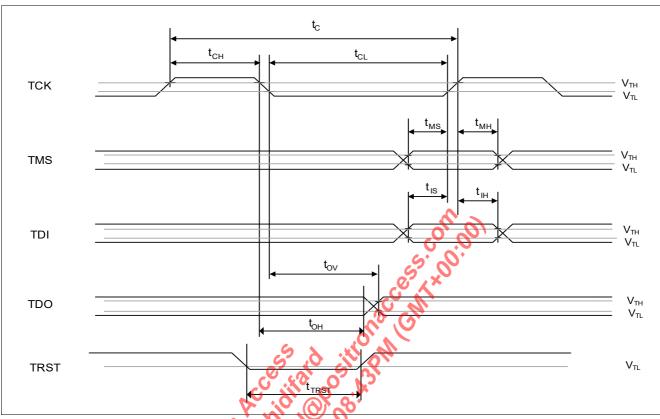

| , , ,        | Debug interace                                                                                                                                                                                                                                                                                                                                                      | 90 |

# 10G PON Chipset PRX126

| 21.7.1<br>21.7.2<br>21.8     | UART Debug Interface  JTAG Interface  On-chip Packet Buffer                                                                                                                                                                                                                                                                                                                                                                                                         | . 98                                          |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

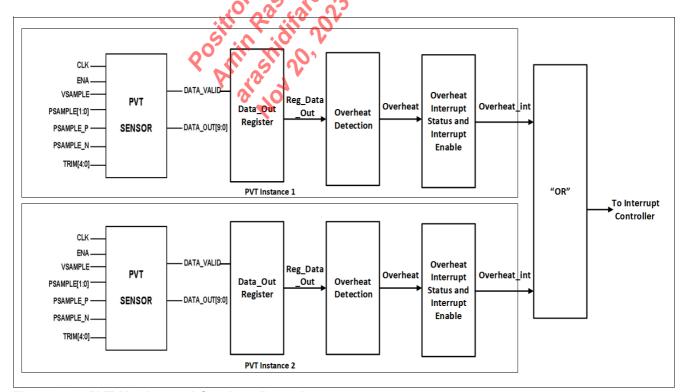

| 22.1<br>22.2<br>22.3<br>22.4 | Power Management  Process, Voltage and Temperature Monitor  Dynamic Voltage Scaling  Adaptive and Static Frequency Scaling and Clock Gating  Smart On-Chip and Off-Chip Packet Buffer Allocation                                                                                                                                                                                                                                                                    | . 99<br>100<br>100                            |

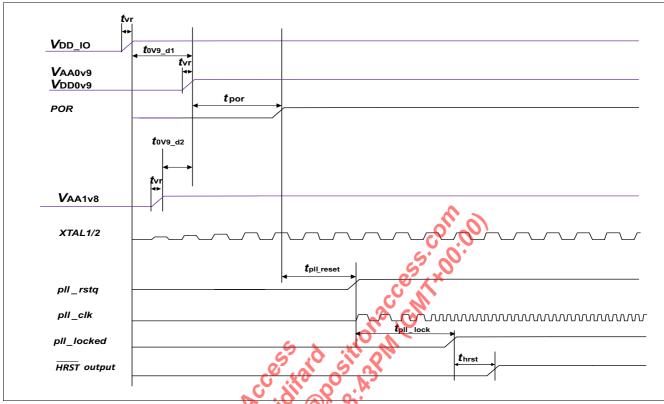

| 23.1<br>23.2<br>23.3         | Electrical Characteristics Absolute Maximum Ratings Operating Range Power Supply Sequencing                                                                                                                                                                                                                                                                                                                                                                         | 101<br>101<br>102                             |

| 23.4<br>23.4.1<br>23.4.2     | Power Dissipation Overview                                                                                                                                                                                                                                                                                                                                                                                                                                          | 104<br>104                                    |

| 23.5<br>23.6<br>23.6.1       | Power Dissipation of Full Performance Use Case  Operating Current  Digital I/O Electrical Characteristics  Digital I/O DC Characteristics  Digital I/O AC Characteristics  DDR Interface Characteristics  DDR Interface DC Characteristics  DDR Interface AC Characteristics  Ethernet SerDes Interface Characteristics  Power-on Reset Detection  Dying Gasp Detection  Built-in Temperature Sensor  Crystal Specification  Differential Input Clock Specification | 106<br>106                                    |

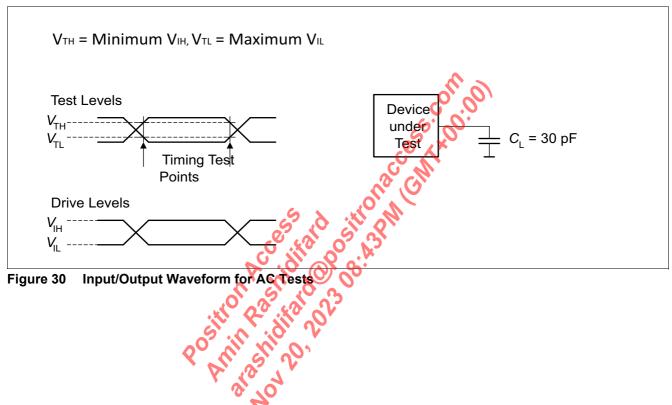

| 23.6.2                       | Digital I/O AC Characteristics  DDR Interface Characteristics                                                                                                                                                                                                                                                                                                                                                                                                       | 100<br>107<br>112                             |

| 23.7.1<br>23.7.2<br>23.8     | DDR Interface DC Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>112</li><li>112</li><li>113</li></ul> |

| 23.9<br>23.10<br>23.11       | Power-on Reset Detection                                                                                                                                                                                                                                                                                                                                                                                                                                            | 114<br>114<br>114                             |

| 23.12<br>23.13               | Crystal Specification                                                                                                                                                                                                                                                                                                                                                                                                                                               | 115<br>115                                    |

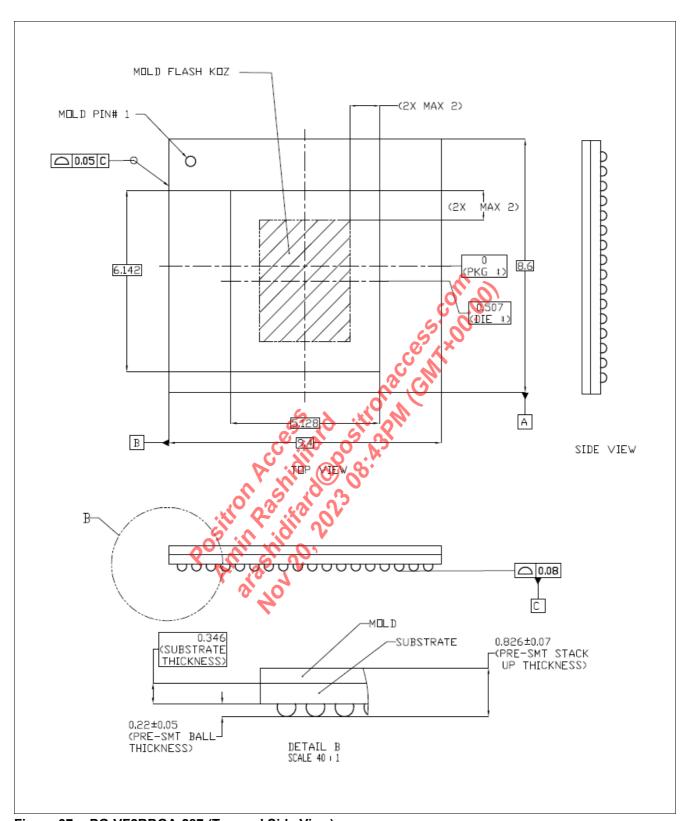

| <b>24</b><br>24.1            | Package Outlines Chip Identification and Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                       | 110                                           |

### **List of Figures**

## **List of Figures**

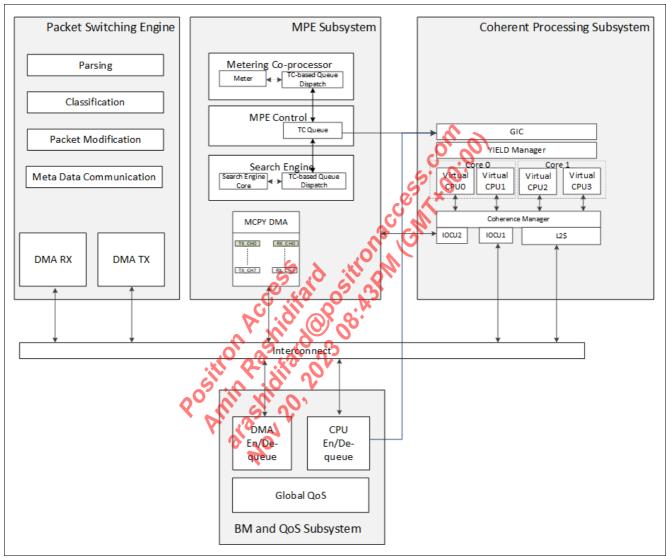

| Figure 1  | PRX126 Block Diagram                                                                                                                                               | 11 |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2  | PRX126 Typical Application                                                                                                                                         | 13 |

| Figure 3  | Ball Diagram for PG-VF2RBGA-287 (Top View)                                                                                                                         | 15 |

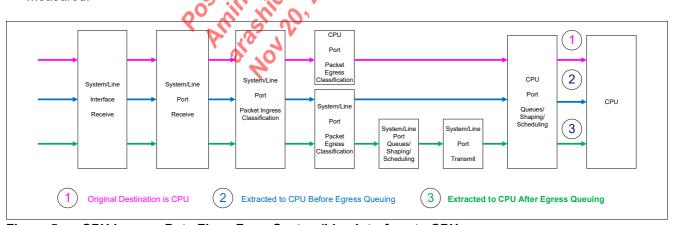

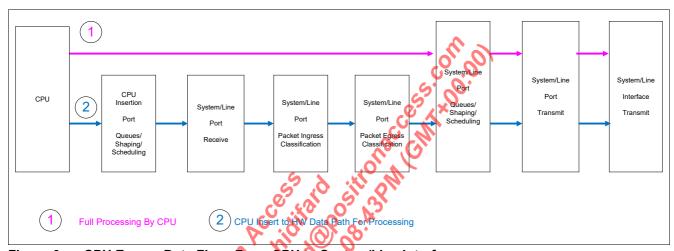

| Figure 4  | PRX126 Data Path Flow                                                                                                                                              | 35 |

| Figure 5  | CPU Ingress Data Flow: From System/Line Interface to CPU                                                                                                           | 38 |

| Figure 6  | CPU Egress Data Flow: From CPU to System/Line Interface                                                                                                            | 39 |

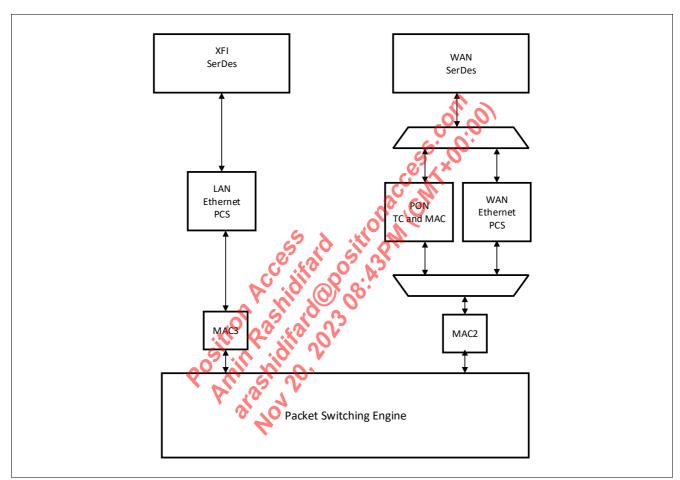

| Figure 7  | SerDes Instances                                                                                                                                                   | 40 |

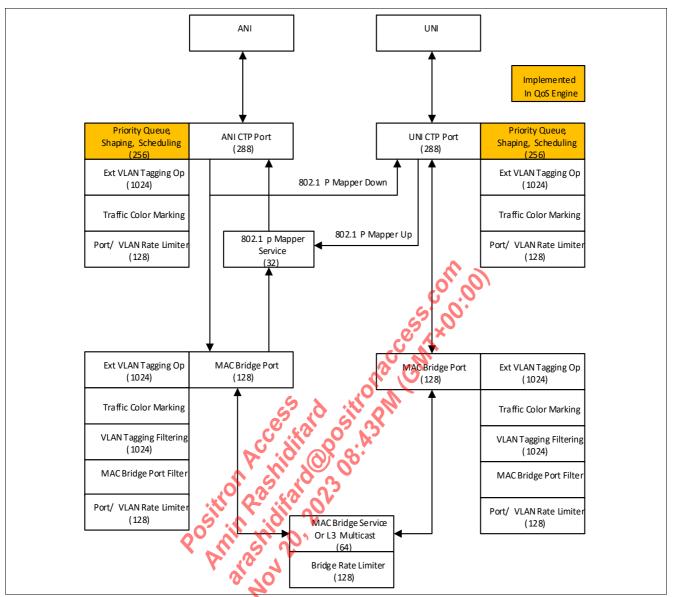

| Figure 8  | OMCI L2 MAC Bridge Implementation                                                                                                                                  | 48 |

| Figure 9  | Traffic Processing Stages                                                                                                                                          | 49 |

| Figure 10 | BM and QoS Architecture                                                                                                                                            | 53 |

| Figure 11 | Overview of the Coherent Processing System                                                                                                                         | 56 |

| Figure 12 | Coherence Manager Overview                                                                                                                                         | 60 |

| Figure 13 | TEE Overview                                                                                                                                                       | 65 |

| Figure 14 | NVM Mapping                                                                                                                                                        | 68 |

| Figure 15 | OTP Data Example                                                                                                                                                   | 69 |

| Figure 16 | Multi-core Processing Engine                                                                                                                                       | 72 |

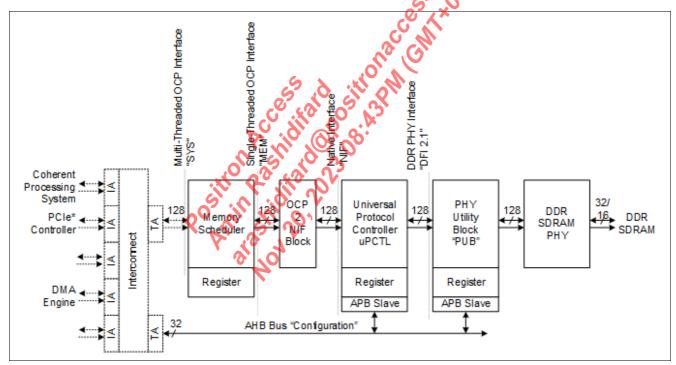

| Figure 17 | NVM Mapping                                                                                                                                                        | 75 |

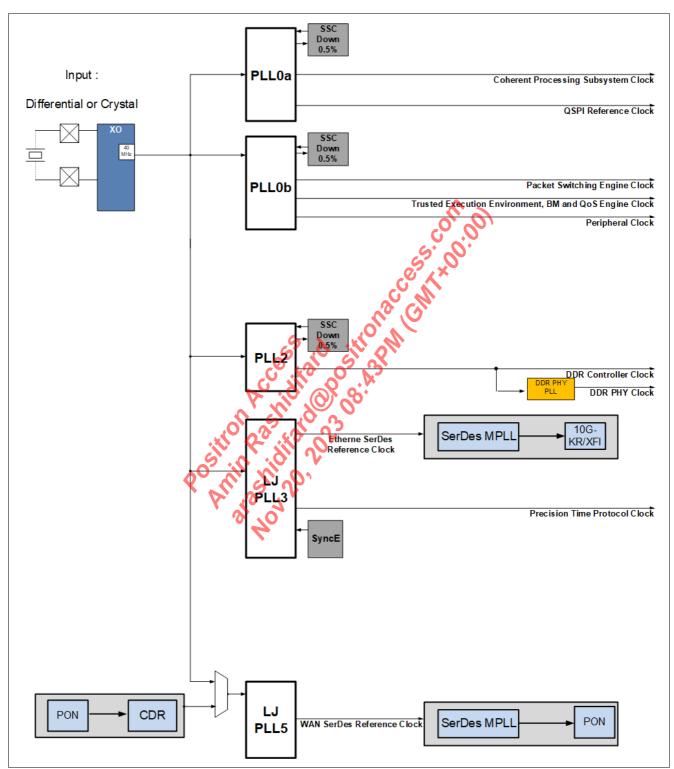

| Figure 18 | Overview of the CGU                                                                                                                                                | 81 |

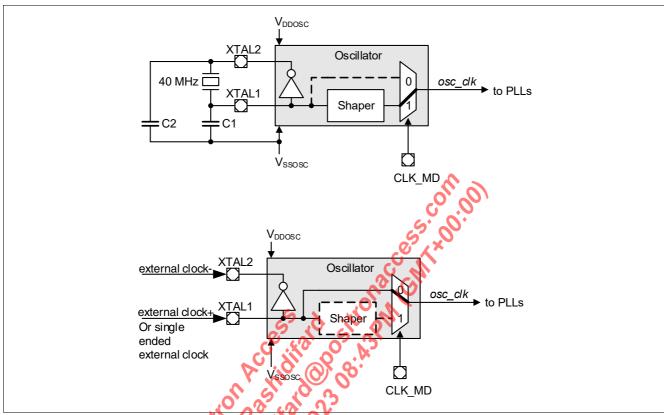

| Figure 19 | Clock Input Options                                                                                                                                                | 82 |

| Figure 20 | Overview of the CGU                                                                                                                                                | 83 |

| Figure 21 | Reset System                                                                                                                                                       | 84 |

| Figure 22 | MPS Interrupt Request Functionality                                                                                                                                | 86 |

| Figure 23 | Reset System .  MPS Interrupt Request Functionality .  MPS2 Interrupt Request Functionality .  ASC/UART System Block Diagram .  GPTC0/1/2 Alternate Input Source . | 87 |